Při zkoumání stavů napájení CPU Core 2 („stavy C "), ve skutečnosti se mi podařilo implementovat podporu pro většinu starších procesorů Intel Core/Core 2. Kompletní implementace (záplata Linuxu) se všemi základními informacemi je zdokumentována zde.

Jak jsem shromažďoval více informací o těchto procesorech, začalo být zřejmé, že C-stavy podporované v modelu (modelech) Core 2 jsou mnohem složitější než u starších i novějších procesorů. Tyto stavy jsou známé jako Vylepšené C-stavy (nebo „CxE "), které zahrnují balíček, jednotlivá jádra a další součásti čipové sady (např. paměť). V době intel_idle Byl vydán ovladač, kód nebyl příliš vyspělý a bylo vydáno několik procesorů Core 2, které měly konfliktní podporu stavu C.

Některé přesvědčivé informace o podpoře stavu C Core 2 Solo/Duo byly nalezeny v tomto článku z roku 2006. Týká se to podpory ve Windows, ale naznačuje to robustní hardwarovou podporu stavu C u těchto procesorů. Informace týkající se Kentsfield jsou v rozporu se skutečným číslem modelu, takže se domnívám, že ve skutečnosti odkazují na níže uvedený Yorkfield:

...čtyřjádrový procesor Intel Core 2 Extreme (Kentsfield) podporuje všech pět technologií pro výkon a úsporu energie — Enhanced IntelSpeedStep (EIST), Thermal Monitor 1 (TM1) a Thermal Monitor 2 (TM2), stará modulace hodin On-Demand ( ODCM), stejně jako Enhanced C States (CxE). Ve srovnání s procesory Intel Pentium 4 a Pentium D 600, 800 a 900, které se vyznačují pouze stavem Enhanced Halt (C1), byla tato funkce u procesorů Intel Core 2 (stejně jako u procesorů Intel Core Solo/Duo) rozšířena o všechny možné klidové stavy procesoru, včetně Stop Grant (C2), Deep Sleep (C3) a DeeperSleep (C4).

Tento článek z roku 2008 popisuje podporu pro stavy C s jedním jádrem u vícejádrových procesorů Intel, včetně Core 2 Duo a Core 2 Quad (další užitečné informace na pozadí byly nalezeny v této bílé knize od společnosti Dell):

C-stav jádra je hardwarový C-stav. Existuje několik základních nečinných stavů, např. CC1 a CC3. Jak víme, moderní moderní procesor má více jader, jako například nedávno vydané mobilní procesory Core DuoT5000/T7000, v některých kruzích známé jako Penryn. To, co jsme dříve považovali za CPU / procesor, má ve skutečnosti vedle sebe víceúčelové CPU. Intel Core Duo má v procesorovém čipu 2 jádra. Intel Core-2 Quad má 4 taková jádra procesorového čipu. Každé z těchto jader má svůj vlastní klidový stav. To dává smysl, protože jedno jádro může být nečinné, zatímco jiné tvrdě pracuje na vláknu. Stav C jádra je tedy klidový stav jednoho z těchto jader.

Našel jsem prezentaci z roku 2010 od Intelu, která poskytuje další informace o intel_idle ovladač, ale bohužel nevysvětluje nedostatek podpory pro Core 2:

Tento EXPERIMENTÁLNÍ ovladač nahrazuje acpi_idle na procesorech Intel Atom, Intel Core i3/i5/i7 a souvisejících procesorech Intel Xeon. Nepodporuje procesor Intel Core2 nebo starší.

Výše uvedená prezentace ukazuje, že intel_idle ovladač je implementace "menu" CPU Governor, která má vliv na konfiguraci jádra Linuxu (tj. CONFIG_CPU_IDLE_GOV_LADDER vs. CONFIG_CPU_IDLE_GOV_MENU ). Rozdíly mezi regulátory žebříčku a menu jsou stručně popsány v této odpovědi.

Společnost Dell má užitečný článek, který uvádí kompatibilitu C0 až C6 ve stavu C:

Režimy C1 až C3 fungují tak, že v podstatě omezují hodinové signály používané uvnitř CPU, zatímco režimy C4 až C6 pracují tak, že snižují napětí CPU. "Vylepšené" režimy mohou dělat obojí současně.

Mode Name CPUs

C0 Operating State All CPUs

C1 Halt 486DX4 and above

C1E Enhanced Halt All socket LGA775 CPUs

C1E — Turion 64, 65-nm Athlon X2 and Phenom CPUs

C2 Stop Grant 486DX4 and above

C2 Stop Clock Only 486DX4, Pentium, Pentium MMX, K5, K6, K6-2, K6-III

C2E Extended Stop Grant Core 2 Duo and above (Intel only)

C3 Sleep Pentium II, Athlon and above, but not on Core 2 Duo E4000 and E6000

C3 Deep Sleep Pentium II and above, but not on Core 2 Duo E4000 and E6000; Turion 64

C3 AltVID AMD Turion 64

C4 Deeper Sleep Pentium M and above, but not on Core 2 Duo E4000 and E6000 series; AMD Turion 64

C4E/C5 Enhanced Deeper Sleep Core Solo, Core Duo and 45-nm mobile Core 2 Duo only

C6 Deep Power Down 45-nm mobile Core 2 Duo only

Z této tabulky (kterou jsem později v některých případech zjistil jako nesprávnou) se zdá, že existovala řada rozdílů v podpoře stavu C u procesorů Core 2 (Všimněte si, že téměř všechny procesory Core 2 jsou Socket LGA775, kromě Core 2 Solo SU3500, což jsou procesory Socket BGA956 a Merom/Penryn. Procesory „Intel Core“ Solo/Duo jsou jedním ze Socket PBGA479 nebo PPGA478).

Další výjimka z tabulky byla nalezena v tomto článku:

Core 2 Duo E8500 od Intelu podporuje C-stavy C2 a C4, zatímco Core 2Extreme QX9650 nikoli.

Zajímavé je, že QX9650 je procesor Yorkfield (Intel family 6, model 23, steping 6). Pro informaci, můj Q9550S je Intel rodiny 6, model 23 (0x17), krok 10, který údajně podporuje C-state C4 (potvrzeno experimenty). Core 2 Solo U3500 má navíc identické CPUID (rodina, model, krokování) jako Q9550S, ale je k dispozici v patici jiné než LGA775, což zkresluje interpretaci výše uvedené tabulky.

Je jasné, že CPUID musí být použito alespoň po krokování, aby bylo možné identifikovat podporu C-state pro tento model procesoru a v některých případech může být nedostatečná (v tuto chvíli není stanoveno).

Signatura metody pro přiřazení informací o nečinnosti CPU je:

#define ICPU(model, cpu) \

{ X86_VENDOR_INTEL, 6, model, X86_FEATURE_ANY, (unsigned long)&cpu }

Kde model je uveden v asm/intel-family.h. Při zkoumání tohoto souboru záhlaví vidím, že procesorům Intel jsou přiřazeny 8bitové identifikátory, které se zdají odpovídat číslům modelů řady Intel 6:

#define INTEL_FAM6_CORE2_PENRYN 0x17

Z výše uvedeného máme Intel Family 6, Model 23 (0x17) definovaný jako INTEL_FAM6_CORE2_PENRYN . To by mělo stačit pro definování klidových stavů pro většinu procesorů Model 23, ale mohlo by to způsobit problémy s QX9650, jak je uvedeno výše.

Minimálně každá skupina procesorů, která má odlišnou sadu C-stavů, by tedy musela být definována v tomto seznamu.

Zagacki a Ponnala, Intel Technology Journal 12 (3):219-227, 2008 naznačují, že procesory Yorkfield skutečně podporují C2 a C4. Také se zdá, že naznačují, že specifikace ACPI 3.0a podporuje přechody pouze mezi C-stavy C0, C1, C2 a C3, což, jak předpokládám, může také omezovat Linux acpi_idle ovladače k přechodům mezi touto omezenou sadou C-stavů. Tento článek však naznačuje, že tomu tak nemusí být vždy:

Mějte na paměti, že jde o stav ACPI C, nikoli stav procesoru, takže ACPIC3 může být HW C6 atd.

Také poznámka:

Kromě samotného procesoru, protože C4 je synchronizované úsilí mezi hlavními křemíkovými součástmi platformy, Intel Q45 ExpressChipset dosahuje 28procentního zlepšení výkonu.

Čipová sada, kterou používám, je skutečně čipová sada Intel Q45 Express.

Dokumentace Intel o stavech MWAIT je stručná, ale potvrzuje chování ACPI specifické pro BIOS:

C-stavy specifické pro procesor definované v rozšířeních MWAIT lze mapovat na typy C-stavů definované ACPI (C0, C1, C2, C3). Vztah mapování závisí na definici stavu C implementací procesoru a je vystaven OSPM systémem BIOS pomocí tabulky _CST definované ACPI.

Moje interpretace výše uvedené tabulky (v kombinaci s tabulkou z Wikipedie, asm/intel-family.h a výše uvedených článků) je:

Model 9 0x09 (Pentium M a Celeron M ):

- Banias:C0, C1, C2, C3, C4

Model 13 0x0D (Pentium M a Celeron M ):

- Dothan, Stealey:C0, C1, C2, C3, C4

Model 14 0x0E INTEL_FAM6_CORE_YONAH (Enhanced Pentium M , Vylepšený Celeron M nebo Intel Core ):

- Yonah (Core Solo , Core Duo ):CO, C1, C2, C3, C4, C4E/C5

Model 15 0x0F INTEL_FAM6_CORE2_MEROM (některé Core 2 a Dvoujádrový procesor Pentium ):

- Kentsfield, Merom, Conroe, Allendale (E2xxx/E4xxx a Core 2 Duo E6xxx, T7xxxx/T8xxxx , Core 2 Extreme QX6xxx , Core 2 Quad Q6xxx ):C0, C1, C1E, C2, C2E

Model 23 0x17 INTEL_FAM6_CORE2_PENRYN (Core 2 ):

- Merom-L/Penryn-L:?

- Penryn (Mobil Core 2 Duo 45nm ):C0, C1, C1E, C2, C2E, C3, C4, C4E/C5, C6

- Yorkfield (Core 2 Extreme QX9650 ):C0, C1, C1E, C2E?, C3

- Wolfdale/Yorkfield (Core 2 Quad , C2Q Xeon , Core 2 Duo E5xxx/E7xxx/E8xxx , Pentium Dual-Core E6xxx , Celeron Dual-Core ):C0, C1, C1E, C2, C2E, C3, C4

Z množství rozmanitosti podpory C-stavů v rámci pouze řady procesorů Core 2 se zdá, že nedostatek konzistentní podpory pro C-stavy mohl být důvodem, proč se je nepokusit plně podporovat prostřednictvím intel_idle Řidič. Rád bych úplně dokončil výše uvedený seznam pro celou řadu Core 2.

To ve skutečnosti není uspokojivá odpověď, protože mě nutí přemýšlet, kolik zbytečné energie je spotřebováno a přebytečné teplo bylo (a stále je) generováno tím, že plně nevyužívají robustní energeticky úsporné MWAIT C-states na těchto procesorech.

Chattopadhyay et al. 2018, Energeticky účinné vysoce výkonné procesory:Nedávné přístupy k navrhování ekologických vysoce výkonných počítačů stojí za zmínku pro specifické chování, které hledám u čipové sady Q45 Express:

Package C-state (PC0-PC10) – Když jsou výpočetní domény, Core a Graphics (GPU) nečinné, má procesor příležitost pro další úspory energie na úrovni jádra a platformy, například propláchnutím LLC a napájením řadiče paměti. a DRAM IO a v určitém stavu může být celý procesor vypnutý, zatímco jeho stav je zachován v doméně vždy zapnutého napájení.

Jako test jsem vložil následující na linux/drivers/idle/intel_idle.c řádek 127:

static struct cpuidle_state conroe_cstates[] = {

{

.name = "C1",

.desc = "MWAIT 0x00",

.flags = MWAIT2flg(0x00),

.exit_latency = 3,

.target_residency = 6,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.name = "C1E",

.desc = "MWAIT 0x01",

.flags = MWAIT2flg(0x01),

.exit_latency = 10,

.target_residency = 20,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

// {

// .name = "C2",

// .desc = "MWAIT 0x10",

// .flags = MWAIT2flg(0x10),

// .exit_latency = 20,

// .target_residency = 40,

// .enter = &intel_idle,

// .enter_s2idle = intel_idle_s2idle, },

{

.name = "C2E",

.desc = "MWAIT 0x11",

.flags = MWAIT2flg(0x11),

.exit_latency = 40,

.target_residency = 100,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.enter = NULL }

};

static struct cpuidle_state core2_cstates[] = {

{

.name = "C1",

.desc = "MWAIT 0x00",

.flags = MWAIT2flg(0x00),

.exit_latency = 3,

.target_residency = 6,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.name = "C1E",

.desc = "MWAIT 0x01",

.flags = MWAIT2flg(0x01),

.exit_latency = 10,

.target_residency = 20,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.name = "C2",

.desc = "MWAIT 0x10",

.flags = MWAIT2flg(0x10),

.exit_latency = 20,

.target_residency = 40,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.name = "C2E",

.desc = "MWAIT 0x11",

.flags = MWAIT2flg(0x11),

.exit_latency = 40,

.target_residency = 100,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.name = "C3",

.desc = "MWAIT 0x20",

.flags = MWAIT2flg(0x20) | CPUIDLE_FLAG_TLB_FLUSHED,

.exit_latency = 85,

.target_residency = 200,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.name = "C4",

.desc = "MWAIT 0x30",

.flags = MWAIT2flg(0x30) | CPUIDLE_FLAG_TLB_FLUSHED,

.exit_latency = 100,

.target_residency = 400,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.name = "C4E",

.desc = "MWAIT 0x31",

.flags = MWAIT2flg(0x31) | CPUIDLE_FLAG_TLB_FLUSHED,

.exit_latency = 100,

.target_residency = 400,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.name = "C6",

.desc = "MWAIT 0x40",

.flags = MWAIT2flg(0x40) | CPUIDLE_FLAG_TLB_FLUSHED,

.exit_latency = 200,

.target_residency = 800,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.enter = NULL }

};

na intel_idle.c řádek 983:

static const struct idle_cpu idle_cpu_conroe = {

.state_table = conroe_cstates,

.disable_promotion_to_c1e = false,

};

static const struct idle_cpu idle_cpu_core2 = {

.state_table = core2_cstates,

.disable_promotion_to_c1e = false,

};

na intel_idle.c řádek 1073:

ICPU(INTEL_FAM6_CORE2_MEROM, idle_cpu_conroe),

ICPU(INTEL_FAM6_CORE2_PENRYN, idle_cpu_core2),

Po rychlé kompilaci a restartu mých uzlů PXE, dmesg nyní ukazuje:

[ 0.019845] cpuidle: using governor menu

[ 0.515785] clocksource: acpi_pm: mask: 0xffffff max_cycles: 0xffffff, max_idle_ns: 2085701024 ns

[ 0.543404] intel_idle: MWAIT substates: 0x22220

[ 0.543405] intel_idle: v0.4.1 model 0x17

[ 0.543413] tsc: Marking TSC unstable due to TSC halts in idle states deeper than C2

[ 0.543680] intel_idle: lapic_timer_reliable_states 0x2

A nyní se PowerTOP zobrazuje:

Package | CPU 0

POLL 2.5% | POLL 0.0% 0.0 ms

C1E 2.9% | C1E 5.0% 22.4 ms

C2 0.4% | C2 0.2% 0.2 ms

C3 2.1% | C3 1.9% 0.5 ms

C4E 89.9% | C4E 92.6% 66.5 ms

| CPU 1

| POLL 10.0% 400.8 ms

| C1E 5.1% 6.4 ms

| C2 0.3% 0.1 ms

| C3 1.4% 0.6 ms

| C4E 76.8% 73.6 ms

| CPU 2

| POLL 0.0% 0.2 ms

| C1E 1.1% 3.7 ms

| C2 0.2% 0.2 ms

| C3 3.9% 1.3 ms

| C4E 93.1% 26.4 ms

| CPU 3

| POLL 0.0% 0.7 ms

| C1E 0.3% 0.3 ms

| C2 1.1% 0.4 ms

| C3 1.1% 0.5 ms

| C4E 97.0% 45.2 ms

Konečně jsem se dostal ke stavům Enhanced Core 2 C a vypadá to, že došlo k měřitelnému poklesu spotřeby energie – můj měřič na 8 uzlech se zdá být v průměru nejméně o 5 % nižší (s jedním uzlem stále běžícím se starým jádrem) , ale zkusím znovu vyměnit jádra jako test.

Zajímavá poznámka ohledně podpory C4E – zdá se, že můj procesor Yorktown Q9550S ji podporuje (nebo nějaký jiný podstav C4), jak je doloženo výše! To mě mate, protože datasheet Intel na procesoru Core 2 Q9000 (část 6.2) uvádí pouze C-states Normal (C0), HALT (C1 =0x00), Extended HALT (C1E =0x01), Stop Grant (C2 =0x10) , prodloužené povolení zastavení (C2E =0x11), spánek/hluboký spánek (C3 =0x20) a hlubší spánek (C4 =0x30). Jaký je tento dodatečný stav 0x31? Pokud povolím stav C2, pak se místo C4 použije C4E. Pokud zakážu stav C2 (vynucení stavu C2E), použije se místo C4E C4. Mám podezření, že to může mít něco společného s příznaky MWAIT, ale zatím jsem nenašel dokumentaci pro toto chování.

Nejsem si jistý, co si o tom mám myslet:Zdá se, že stav C1E se používá místo C1, C2 se používá místo C2E a C4E se používá místo C4. Nejsem si jistý, zda lze C1/C1E, C2/C2E a C4/C4E použít společně s intel_idle nebo jsou-li nadbytečné. V této prezentaci z roku 2010 od Intel Labs Pittsburgh jsem našel poznámku, která uvádí, že přechody jsou C0 - C1 - C0 - C1E - C0, a dále uvádí:

C1E se používá pouze tehdy, když jsou všechna jádra v C1E

Domnívám se, že je to třeba interpretovat tak, že stav C1E je zadán na jiných komponentách (např. paměti) pouze tehdy, když jsou všechna jádra ve stavu C1E. Beru to také tak, že to platí ekvivalentně pro stavy C2/C2E a C4/C4E (ačkoli C4E se označuje jako „C4E/C5“, takže si nejsem jistý, zda je C4E podstavem C4 nebo zda je C5 podstavem stav C4E. Zdá se, že testování ukazuje, že C4/C4E je správný). Mohu vynutit použití C2E komentováním stavu C2 - to však způsobí, že se místo C4E použije stav C4 (zde může být zapotřebí více práce). Doufejme, že neexistují žádné procesory model 15 nebo model 23, které by postrádaly stav C2E, protože tyto procesory by byly s výše uvedeným kódem omezeny na C1/C1E.

Také příznaky, latence a hodnoty rezidence by pravděpodobně mohly být vyladěny, ale zdá se, že pouhé kvalifikované odhady založené na hodnotách nečinnosti Nehalemu fungují dobře. K provedení jakýchkoli vylepšení bude zapotřebí více čtení.

Testoval jsem to na Core 2 Duo E2220 (Allendale), Dual Core Pentium E5300 (Wolfdale), Core 2 Duo E7400, Core 2 Duo E8400 (Wolfdale), Core 2 Quad Q9550S (Yorkfield) a Core 2, Extreme a IX9 nenašli žádné problémy kromě výše uvedené preference pro stav C2/C2E a C4/C4E.

Tato úprava ovladače se nevztahuje:

- Původní Core Solo/Core Duo (Yonah, jiné než Core 2) jsou rodiny 6, model 14. To je dobré, protože podporovaly C-stavy C4E/C5 (Enhanced Deep Sleep), ale ne C1E/C2E a bude potřebovat vlastní definici nečinnosti.

Jediné problémy, které mě napadají, jsou:

- Core 2 Solo SU3300/SU3500 (Penryn-L) jsou řady 6, model 23 a budou detekovány tímto ovladačem. Nejedná se však o Socket LGA775, takže nemusí podporovat C-state Enhanced Halt C1E. Stejně tak pro Core 2 Solo ULV U2100/U2200 (Merom-L). Nicméně

intel_idleZdá se, že ovladač vybírá vhodný C1/C1E na základě hardwarové podpory podstavů. - Core 2 Extreme QX9650 (Yorkfield) údajně nepodporuje C-state C2 nebo C4. Potvrdil jsem to nákupem použitého procesoru Optiplex 780 a QX9650 Extreme na eBay. Procesor podporuje C-stavy C1 a C1E. Při této úpravě ovladače je CPU nečinný ve stavu C1E místo C1, takže pravděpodobně dojde k nějaké úspoře energie. Očekával jsem, že uvidím C-state C3, ale při použití tohoto ovladače není přítomen, takže možná budu muset prozkoumat toto dále.

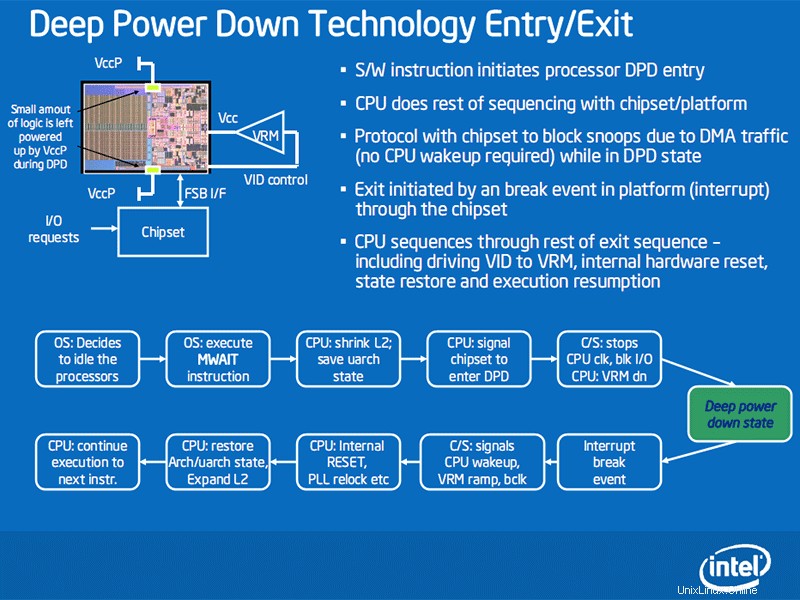

Podařilo se mi najít snímek z prezentace Intel z roku 2009 o přechodech mezi stavy C (tj. Deep Power Down):

Na závěr se ukazuje, že pro nedostatek podpory Core 2 v intel_idle nebyl žádný skutečný důvod Řidič. Nyní je jasné, že původní útržkový kód pro "Core 2 Duo" zpracovával pouze C-stavy C1 a C2, což by bylo mnohem méně efektivní než acpi_idle funkce, která také zpracovává C-stav C3. Jakmile jsem věděl, kde hledat, implementace podpory byla snadná. Užitečné komentáře a další odpovědi byly velmi oceněny, a pokud Amazon poslouchá, víte, kam poslat šek.

Tato aktualizace byla schválena pro github. Brzy pošlu e-mailem opravu LKML.

Aktualizovat :Také se mi podařilo vykopat Socket T/LGA775 Allendale (Conroe) Core 2 Duo E2220, což je rodina 6, model 15, takže jsem přidal podporu i pro to. Tento model postrádá podporu pro C-state C4, ale podporuje C1/C1E a C2/C2E. To by mělo fungovat i pro další čipy založené na Conroe (E4xxx/E6xxx) a možná všechny procesory Kentsfield a Merom (ne Merom-L).

Aktualizovat :Konečně jsem našel nějaké zdroje pro ladění MWAIT. Tento zápis Power vs. Performance a tento stav Deeper C a blogový příspěvek se zvýšenou latencí obsahují některé užitečné informace o identifikaci nečinnosti CPU. Bohužel to hlásí pouze ty výstupní latence, které byly zakódovány v jádře (ale je zajímavé, že pouze stavy hardwaru podporované procesorem):

# cd /sys/devices/system/cpu/cpu0/cpuidle

# for state in `ls -d state*` ; do echo c-$state `cat $state/name` `cat $state/latency` ; done

c-state0/ POLL 0

c-state1/ C1 3

c-state2/ C1E 10

c-state3/ C2 20

c-state4/ C2E 40

c-state5/ C3 20

c-state6/ C4 60

c-state7/ C4E 100

Aktualizace: Zaměstnanec Intelu nedávno publikoval článek na intel_idle podrobně popisující stavy MWAIT.

Existuje vhodnější způsob, jak nakonfigurovat jádro pro optimální podporu nečinnosti CPU pro tuto rodinu procesorů (kromě deaktivace podpory pro intel_idle)

Máte povoleno ACPI a zkontrolovali jste, že se acpi_idle používá. Upřímně pochybuji, že jste vynechali nějakou užitečnou možnost konfigurace jádra. Vždy můžete zkontrolovat powertop pro možné návrhy, ale pravděpodobně jste to již věděli.

Toto není odpověď, ale chci ji naformátovat :-(.

Podíváme-li se na zdrojový kód jádra, aktuální ovladač intel_idle obsahuje test, který konkrétně vyloučí Intel rodinu 6 z ovladače.

Ne, není :-).

id = x86_match_cpu(intel_idle_ids);

if (!id) {

if (boot_cpu_data.x86_vendor == X86_VENDOR_INTEL &&

boot_cpu_data.x86 == 6)

pr_debug(PREFIX "does not run on family %d model %d\n",

boot_cpu_data.x86, boot_cpu_data.x86_model);

return -ENODEV;

}

if příkaz nevylučuje rodinu 6. Místo toho if příkaz poskytuje při povolení ladění zprávu, že tento konkrétní moderní procesor Intel není podporován intel_idle . Ve skutečnosti je můj současný CPU i5-5300U Family 6 a používá intel_idle .

Co vylučuje váš CPU je, že v intel_idle_ids není žádná shoda tabulka.

Všiml jsem si tohoto potvrzení, které implementovalo tabulku. Kód, který odstraňuje, měl switch místo toho prohlášení. Díky tomu lze snadno zjistit, že nejstarší model intel_idle byl implementován/úspěšně testován/cokoli je 0x1A =26. https://github.com/torvalds/linux/commit/b66b8b9a4a79087dde1b358a016e5c8639ccf1>

Mám podezření, že by to mohl být jen případ příležitosti a nákladů. Když intel_idle Bylo přidáno, zdá se, že podpora Core 2 Duo byla plánována, ale nikdy nebyla plně implementována – možná, když se k tomu inženýři Intelu dostali, už to nestálo za to. Rovnice je poměrně složitá:intel_idle musí poskytovat dostatečné výhody oproti acpi_idle aby to stálo za to podporovat zde, na CPU, které uvidí „vylepšené“ jádro v dostatečném počtu...

Jak říká odpověď sourcejedi, ovladač nevylučuje celou rodinu 6. intel_idle inicializační kontroly CPU v seznamu modelů CPU, pokrývající v podstatě všechny mikroarchitektury od Nehalemu po Kaby Lake. Yorkfield je starší než ten (a výrazně odlišný – Nehalem je velmi odlišný od architektur, které před ním byly). Test rodiny 6 ovlivňuje pouze to, zda se chybová zpráva vytiskne; její účinek je pouze v tom, že chybová zpráva se zobrazí pouze na procesorech Intel, nikoli na procesorech AMD (řada Intel 6 zahrnuje všechny procesory Intel bez NetBurst od Pentium Pro).

Chcete-li odpovědět na svou konfigurační otázku, můžete úplně vypnout intel_idle , ale nechat to v je také v pořádku (pokud vám nevadí varování).